菲诺克科技推出M12219+FNK5052充电宝无线充应用PCB LAYOUT设计指南

M12219充电宝部分注意

1:PCB 布局及器件整体布局规划

建议客户使用 4 层板绘制,可以提高 PCB 板的整体性能,根据客户的 PCB 整体的结构大小来分布元器件,元器件合理规划,均匀布局,不要让 PCB 某些部位太挤,某些部位太松,考虑到发热器件摆放位置以及如何散热效果更加 理想,TYPE_C, USB 接口和按键按照机构要求可以伸出板边外,其他元器件尽量不要靠近板边摆放;元器件尽量并排排列。

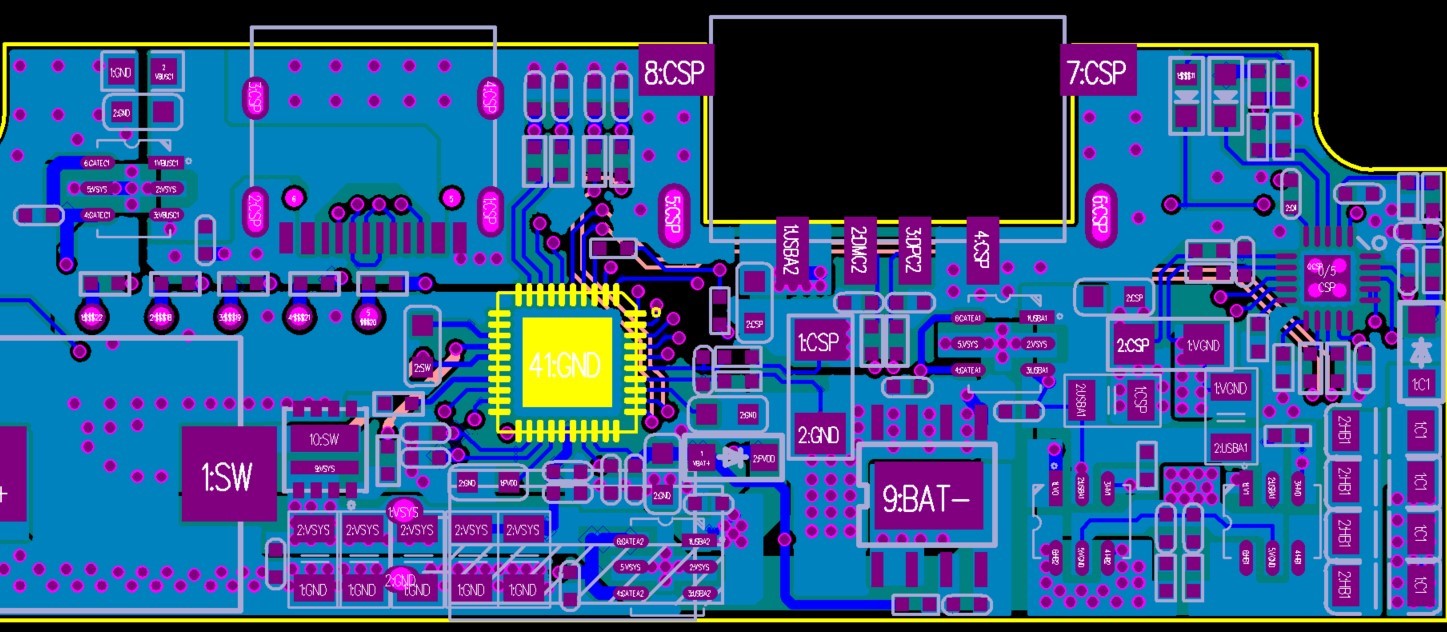

2:M12219 摆放位置

主要考虑 PCB 面积来摆放 M12 系列的 IC 器件的方向,引脚走线来摆放,对于

一般移动电源,M12 系列的 IC 属于核心器件,也属于主要发热器件之一,一般放置于

PCB 的中部,注意调整 M12 系列的朝向,为了更好便于 IC 散热,衬底铺铜开窗并增加

过孔,IC 衬底下尽量不要走线,也便于帮助 IC 散热。

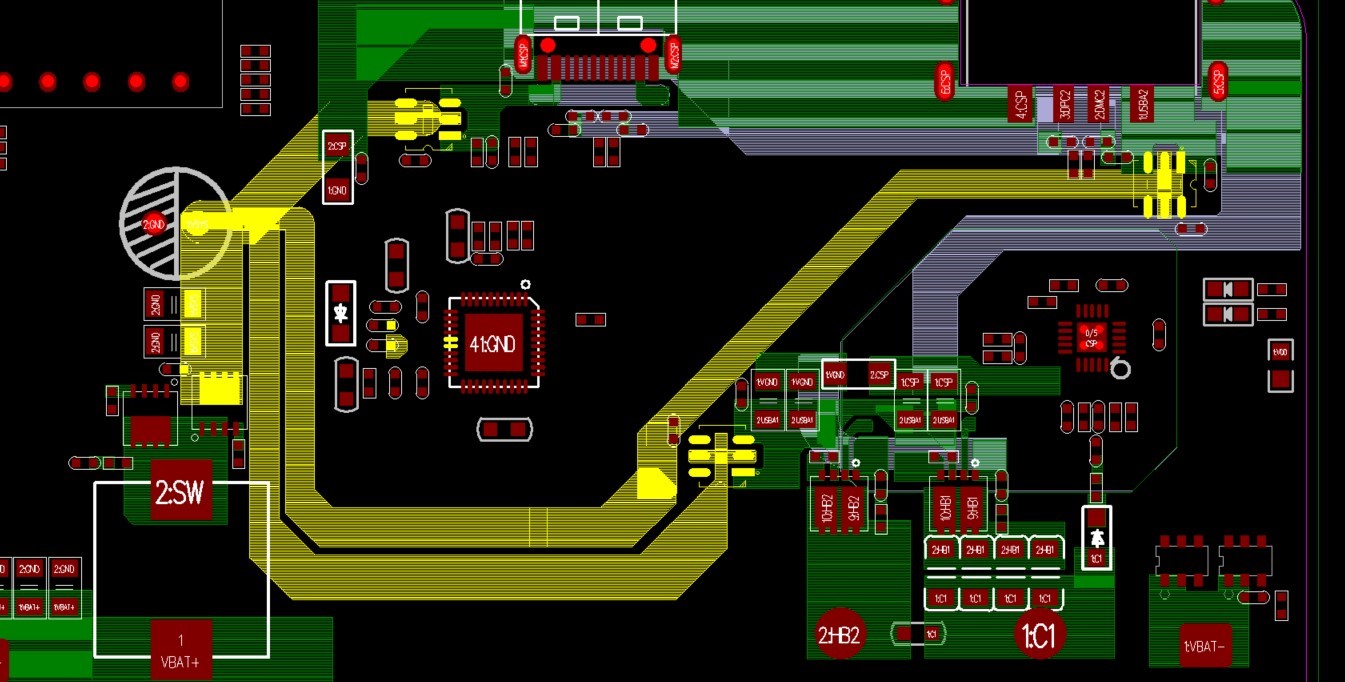

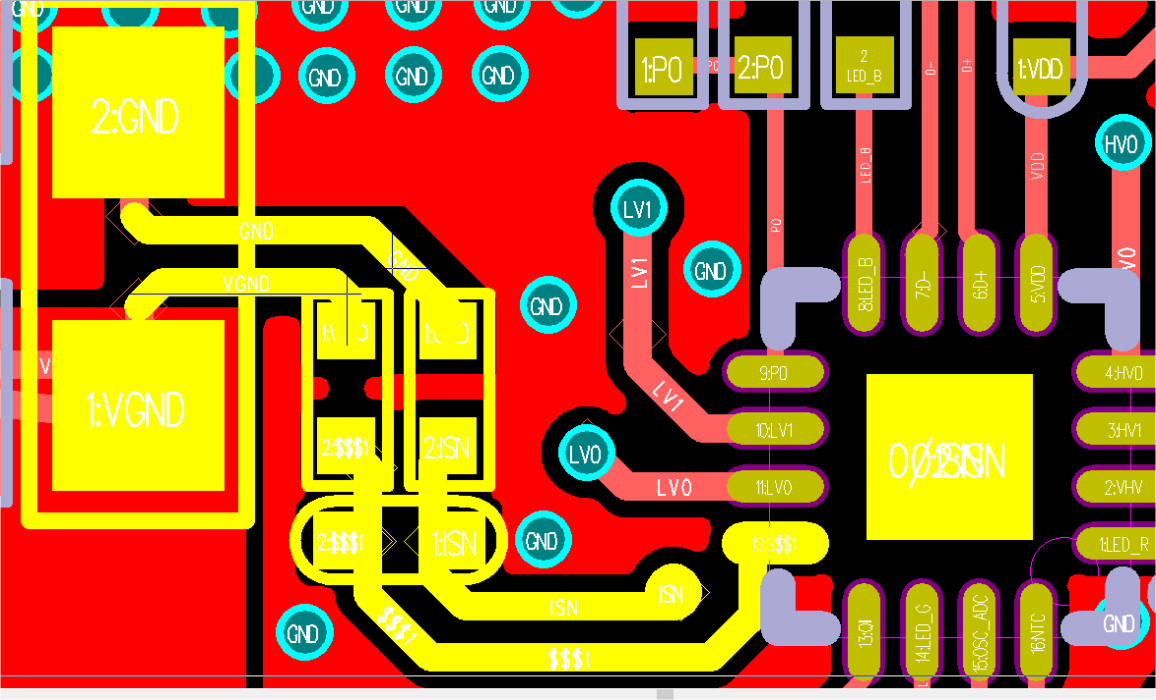

如图1 :

图1

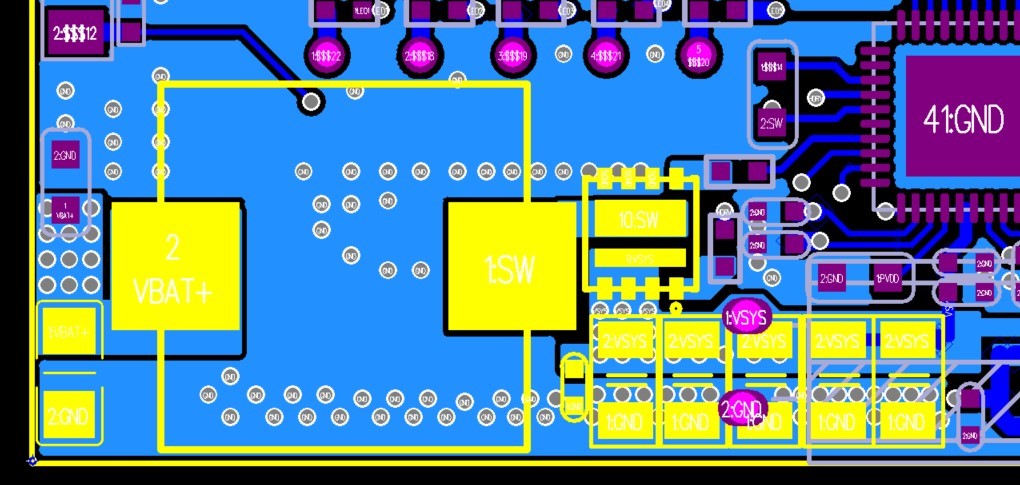

3:升降压 N_MOS 摆放位置

考虑升降压在整机的稳定性和散热效果,以及线路走线要注意以下几点

A:尽可能的把电感 N_MOS放在主控的 25PIN至 36PIN这边的方向方便于走线(HDRV1,

HDRV2,LDRV1,LDRV2),走线 IC 出来不远就到 N_MOS,驱动限流电阻建义放在MOS管的G极附近。整机稳定性也比较好,

也容易过 EMC 认证,输出输入电容尽量和电感MOS放在同一层,输入输出电容负极能直接相通距离尽可能的短,见下图(合封MOS)。

如图2:

图2

B:考虑的散热的问题 N_MOS 及电感要配合好,元器件不能摆放太远,太远会影响到整

机的稳定性和认证,发热元器件摆放尽量远离电感,MOS 选型特别注意,1:内阻小,

2:耐压要有足够的余量,3:N_MOS 的 CISS 和 COSS 电容要小,合适的驱动电压电流.

PCB_LAYOUT 建议

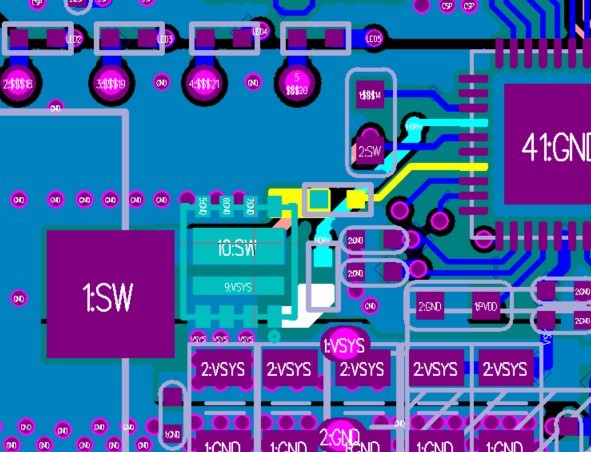

一.功率环路的摆放

功率电路的布局是影响 EMI 最为关键的环路。MOS,电感,输出电容的摆放对于转换效率, EMI 影响很大,对电路的稳定性有至关重要。

布线原则:1、SW 布线面积尽可能的粗而短,上下管 NMOS,电感连接的走线要短,铺铜 面积尽可能的大。2、输入输出电解电容尽量靠近上下管,电解电容正级靠近上管的输出, 电解电容的负极靠近下管的地,使开关环路做到最小。3、SW1,SW2 的 RC 回路靠近 MOS 放置。

二、芯片放置在功率回路的一侧,芯片的中间 PAD 尽可能多的打孔到地。5、MOS 管功率地和电解电容的地,尽可能多的打足够的孔到地,

如图3 图4 :

图3 图4

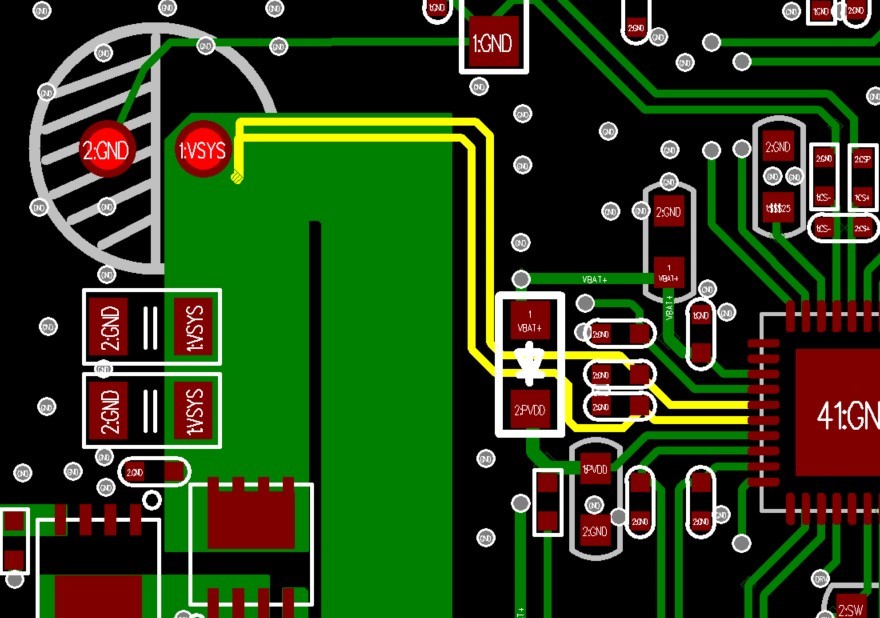

三.对于多口输出布局布线上的SYS处理要注意:每路通路MOS的D极单独从DC/DC滤波电容的正极拉出一条粗线。布局上可以放在端子附近。见下图:

四.插入检测线路处理方式:

主控芯片的P15为供电脚, P16为系统电压检测脚,在线路上是要接同一电平,在布线上要独立拉一条线到VSYS参考点。带载检测主要是能过检测通路MOS的DS电平来实现,所以检测线VBUS要从MOS管的S极拉一条线到芯片引脚,走线时要避开DV/DT和DI/DT的区域。能包地的话最好见下图。

芯片外围电容的放置

AVDD,DVDD,PVDD,VSYS1,VBUSC1,VSYS2,VBUSC2,VBUS3,VBUS4引脚的电容尽量靠近芯片引脚,电容负端尽可能多打孔到地,最短的距离回到芯片底部的地。

芯片 BAT 引脚的电容,用一个 4.7uF 和 104 电容并联到地,尽量靠近芯片引脚,如上图

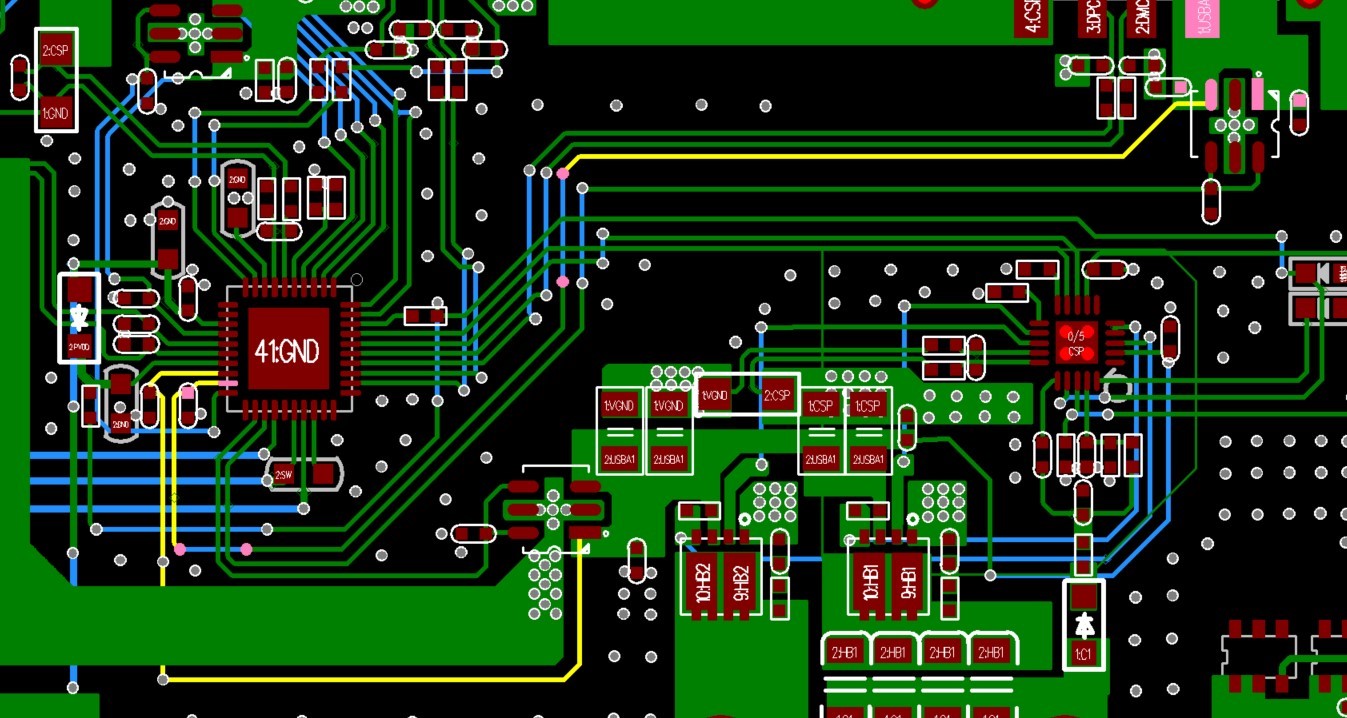

4: BSW PVDD 以及外部线路设计

外部 DC-DC 是给内部芯片供电,并提供 MOS 管驱动电压,DC-DC 的输出尽可能的靠近 PVDD,输出电容靠近 PVDD 引脚,PVDD 引脚对地增加 104 电容。

BSW 出来经靠近主控,然后输出接着电容进入

如图5 图6 :

图5 图6

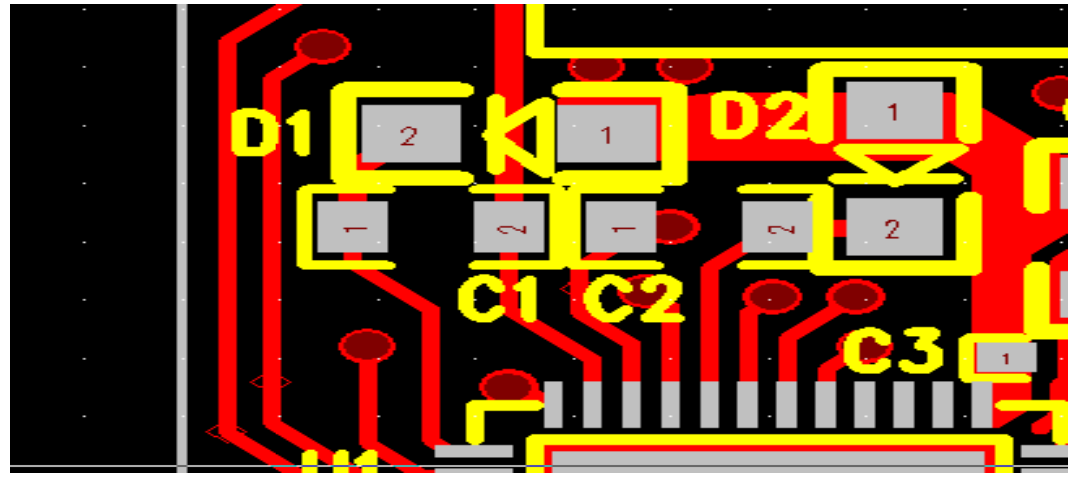

5:BOOT1 BOOT2 电容摆放

BOOT 电容和二极管尽量靠近芯片引脚,尽量同层摆放。BOOT 电容建议使用 0603,二极管建议使用 SOD-323

如图7:

图7

6:采样电阻 SENSE 的摆放及采样走线

采样电阻需要使用 1206 封装并且精度为 1%的合金电阻,电流采样的走线需要间独从电阻两端引出(不能有铺铜覆盖电流走线及过孔),摆放在功率环路离主控可以稍远点,防止温度影响主控,并按差分走线连接至芯片引脚,周边尽量包地,避开DV/DT和DI/DT区域。

如图8:

图8

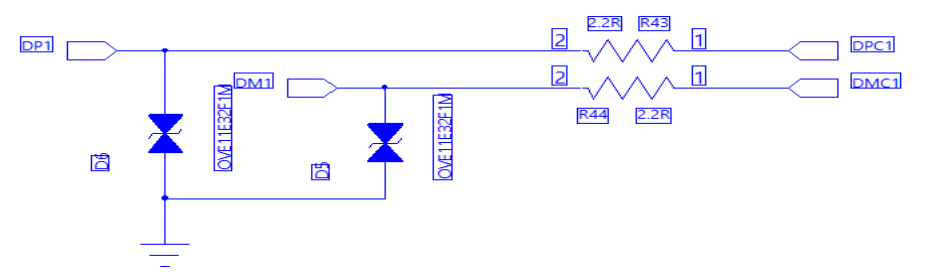

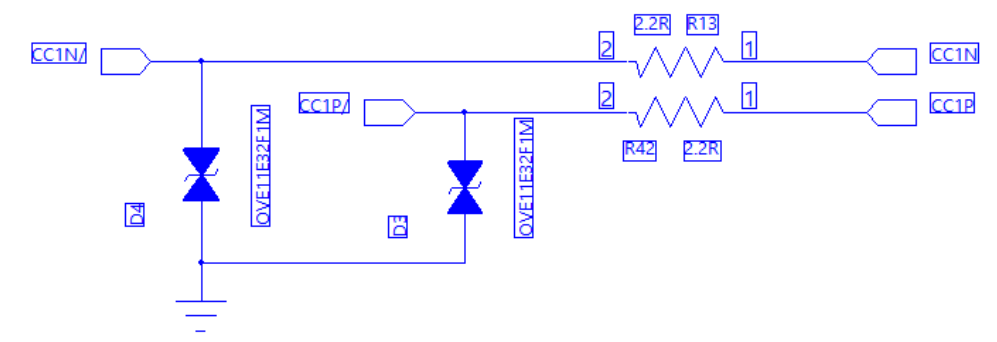

7:CC1N,CC1P,DP,DM 线增加电阻及对地 TVS 管

为了增加 CC1N,CC1P,DP,DM 这四个引脚的搞干扰性及防静电能力,建议在 TYPEC 引脚与芯片引脚之间串电阻,并对地增加双向 TVS 管,DP/DM尽量走差分,ESD尽量放在信号入口处。

如下图9 图10 :

图9

图10

8:电池焊盘 B+、B-的摆放

A:电池保护芯片等发热元器件远离电池

B:电池焊盘要离 MOS 管近,避免效率低线路也要粗减少铜皮阻抗

如图11:

图11

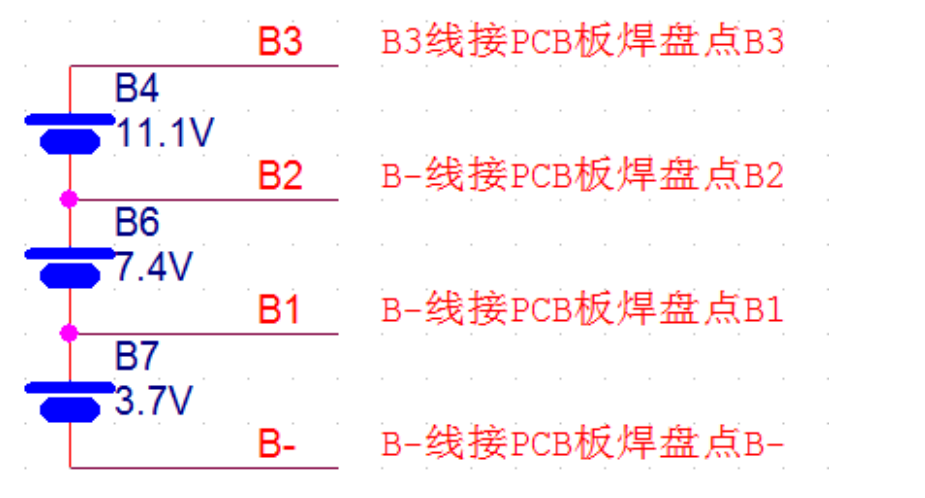

C:电池的焊线顺序是:先焊 B-→B3→B1→B2(在三串的电池 B3 表示 B+)

如图12:

图12

9:电容电阻的布局

输入电容靠近电池端 B+摆放,输出电容靠近 升压 N_MOS 引脚摆放(注意温度的电容, 建议使用 X7R 电容),尽量与 N_MOS 摆同一层尽量避免大电流线路过孔。

M12XX 的 DVDD(1.8V),AVDD(5V),PVDD(5V) ,VIN, VBUS1,VSYS1, , BOOT1,BOOT2

电容靠近 M12 系列 IC 引脚摆放,尽量与 IC 摆同一层,上面 IC 引脚接地电容多打孔

使电容地回流到 IC 衬底,对整机的稳定性以及纹波会有较大的改善功率电阻的摆放,尽量靠近输出 TYPE_C USB 脚线路要粗。

10:LED/ 数码管周边

LED 灯/数码管作为电量显示,功能指示,一般都有机构限制,注意周边器件的距离、

高度,以免干涉或遮光。

11:PCB 固定孔周边

PCB 固定孔用来卡位或固定 PCB,有的还要锁螺丝,注意周边元器件与固定孔的距离,

以免造成干涉或短路。

12:铺铜与走线

A:一般信号走线(不走大电流)建议线宽 0.2MM(8MIL)或 0.25MM(10MIL)。

B: 大电流网络走线, VOUT、SW1,SW2,SYS1、B+、B-、GND 走线尽量宽,最好铺

铜,宽度不小于 2.0MM(约 80MIL);SW1 和 SW2 的走线要尽可能短,尽量不要换层,

大电流网络走线换层时尽量多打过孔,所有输入输出的电容地(GND)回流到 IC 的衬

底,但要同时考虑底层地的完整性,方便散热。

C:PD 数据线 CC1P,CC1N 尽量走线要平行(差分走线),不要经过大电流震荡线路(避

免经过电感下面),否则会出现无法诱骗电压。

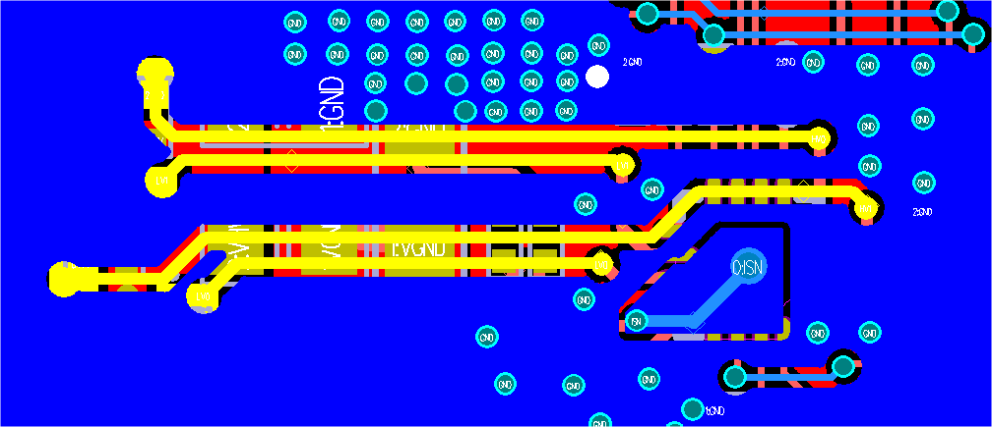

如图13:

图13

D:电流检测线,CSP1 CSN1,CSP2 CSN2,CSP3 CSN3,走线要平行(差分走线)到

USB 输出功率电阻两端(有较多工程师 M12 系列 IC 走线出来直接到 GND,这样是不对

的),不采用电流采样脚接地。

如图14:

13:PCB 铺铜

A:PCB 铺铜不能有多余的死铜、毛刺、突出尖端等

B:过孔、焊盘等必须加泪滴;

C:贴片电容、贴片电阻两端铜箔尽量大小相符,两端受热均匀;

D:固定接口、按键等受力元器件的焊盘周围需要增加铜箔固定适当增加过孔来国定元器件的稳定性;

E:定位孔周围要同一网络(GND)以免打上螺丝和其他网络短路

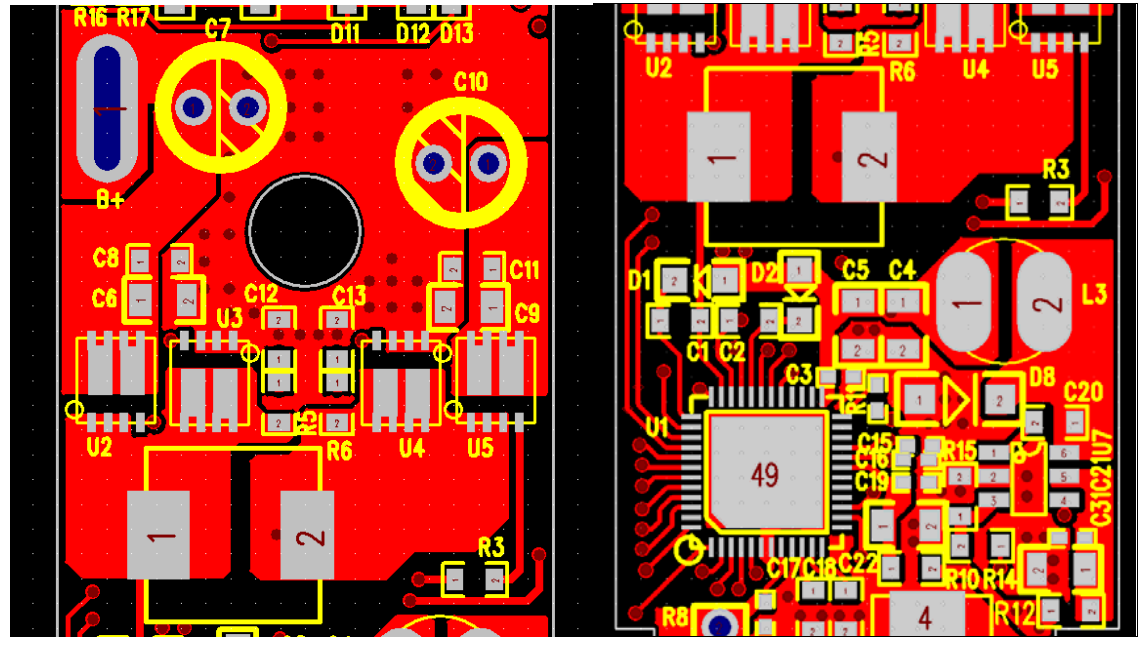

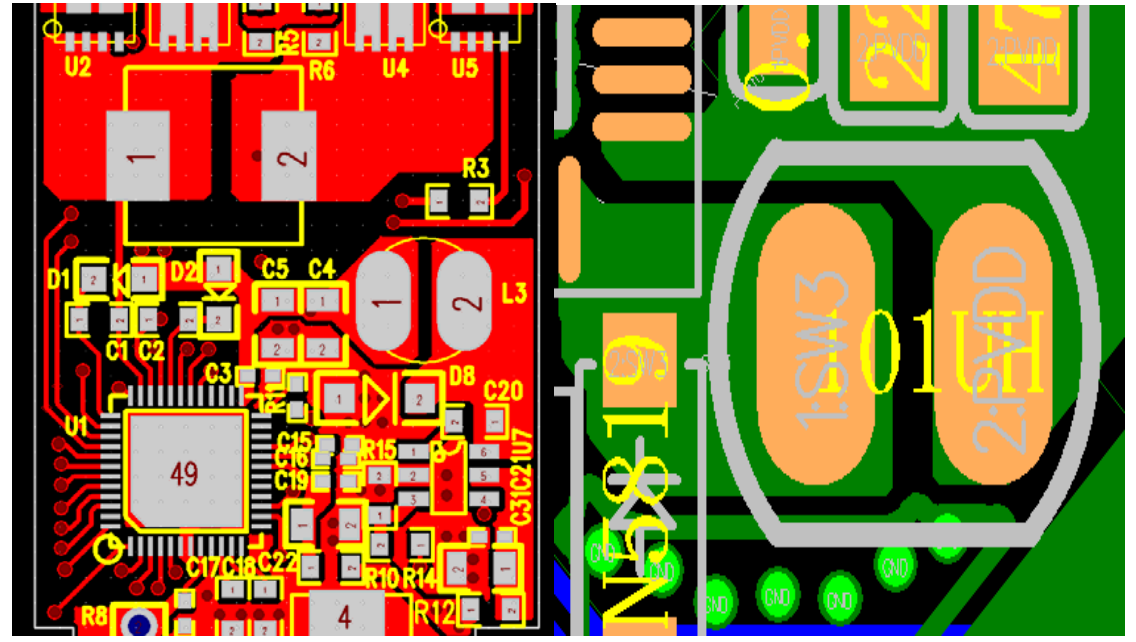

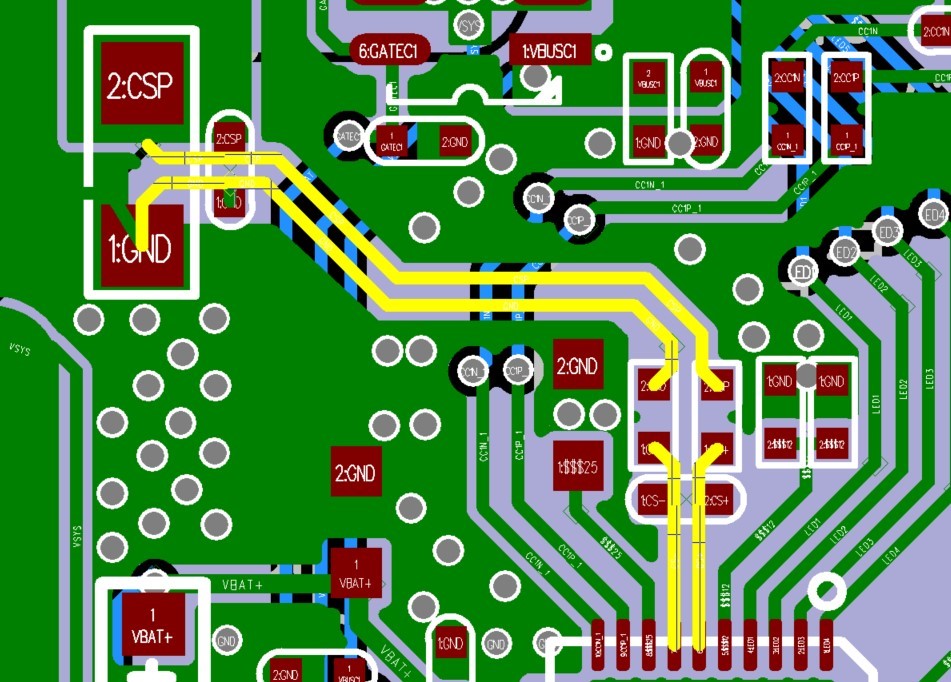

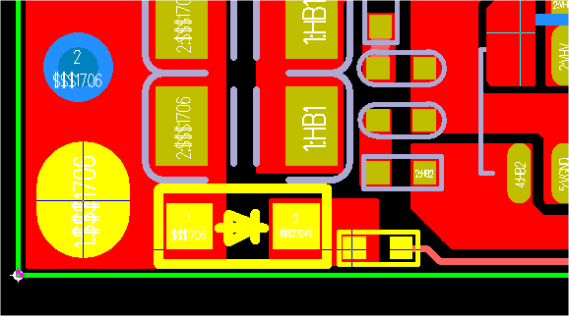

FNK5052无线充布局布线简要说明

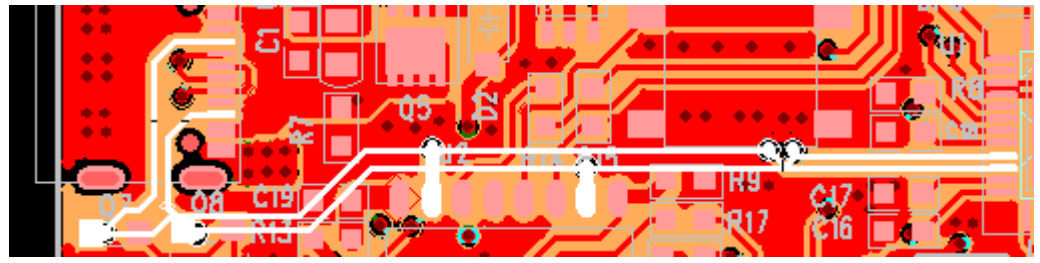

1. 功率MOS管/电流检测电阻/两个滤波电容/芯片摆放尽量靠近.以减小功率环路.检测电阻尽量放在两个电容负极.如下图高亮部分元件:

2. 电流检测信号线尽量差分走线,线宽最小0.25MM,能加粗最好.线尽量短些,滤波的RC靠近FNK5052.如下图高亮部分所示:

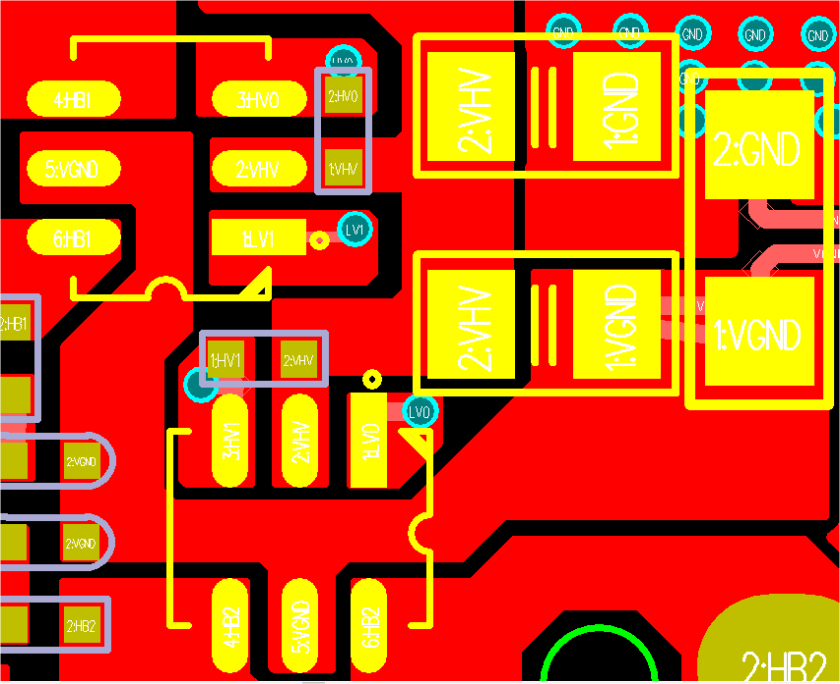

3. FNK FNK5052封装底下的EPAD的焊盘要加过孔,如用一个孔的孔径加到0.5MM以上,如用4到5个的过孔孔径可以小点.布线时在芯片背面能开窗的尽量开窗.

4. 芯片供电线可以走粗点,VHV&VDD滤波电容就近芯片管脚摆放.

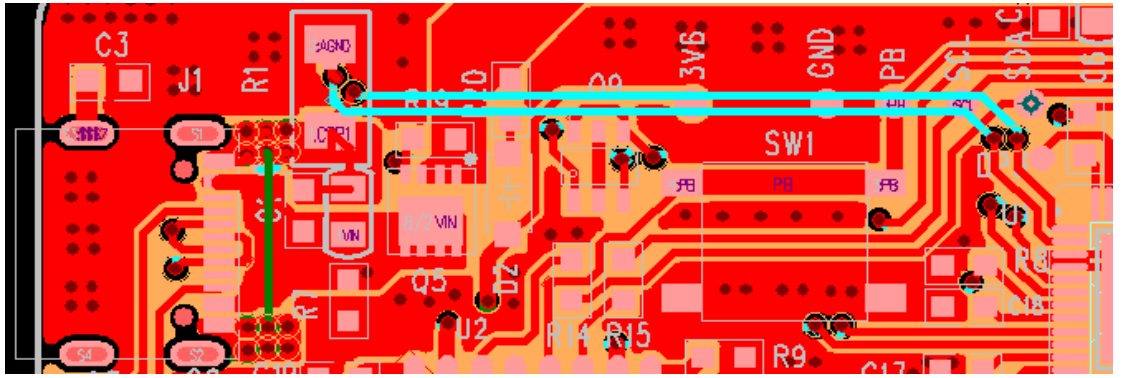

5. 解码电路的检波二极管尽量放在线圈焊点附近,其它元件靠近芯片摆放. 如下图高亮部分:

6. 四路PWM线宽0.2MM以上,走线上尽量包地,线长能短尽量短. 如下图高亮部分所示:

7.布局及走线上尽量优化,确保PCB板一面有大面积连续的地铜皮.